## 12-bit 2-channel 0.5 to 33 MSPS delta-sigma ADC

## **OVERVIEW**

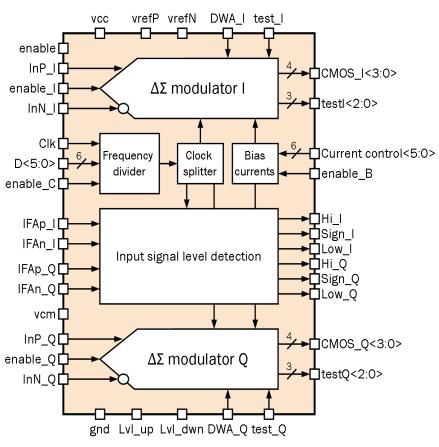

250iHP ADC 04 is second order delta-sigma **ADC** with 5-level quantizer. The block consists of: two integrating cascades based on switch capacitors technique (treats both channels); 5-level flash-ADC (treats both channels); tunable (6-bit control) clock signal frequency divider; clock splitter: block of bias currents, tunable (6-bit control): data-weighted averaging (DWA) correction of capacitors mismatch (treats channels): input signal level detection. Output signal represented in "thermometer" code. There is a possibility to disable of each channel, frequency divider, block of bias currents, DWA correction. There is an in-built output from frequency divider for clocking digital filters. Input DC level is 0.9 V; recommended voltage levels for 0.9  $\pm$  0.4 references are recommended input signal

differential amplitude is 0.64 V; allowable deviation of clock duty cycle:  $50 \pm 5\%$ .

IP technology: iHP SiGe BiCMOS 0.25 um.

IP status: silicon proven.

Area: 0.3mm<sup>2</sup>.

## ELECTRICAL CHARACTERISTICS

| Parameter                               | Symbol                   | Conditions                              |                | Value               |       |                       | TI4   |

|-----------------------------------------|--------------------------|-----------------------------------------|----------------|---------------------|-------|-----------------------|-------|

|                                         |                          |                                         |                | min                 | typ.  | max                   | Units |

| Supply voltage                          | $V_{cc}$                 | -                                       |                | 1.7                 | 1.8   | 1.9                   | V     |

| Operating temperature                   | $T_{j}$                  | -                                       |                | -45                 | +27   | +85                   | °C    |

| Current consumption                     | $I_{cc}$                 | One                                     | @BW = 8  kHz   | 0.232               | 0.239 | 0.272                 | mA    |

|                                         |                          | channel                                 | @BW = 512  kHz | 4.455               | 4.549 | 4.676                 |       |

| Standby current                         | $I_{STB}$                | -                                       |                | 0.68                | 1.86  | 4.01                  | uA    |

| Resolution                              | N                        | -                                       |                | -                   | 12    | -                     | bit   |

| Oversampling ratio                      | OSR                      | -                                       |                | 32                  | -     | -                     | -     |

| Sampling rate                           | Fs                       | -                                       |                | 0.5                 | -     | 33                    | MSPS  |

| Bandwidth                               | BW                       | -                                       |                | 8                   | 128   | 512                   | kHz   |

| Differential peak-to-peak input voltage | $V_{in\_diffp\text{-}p}$ | -<br>  -                                |                | -                   | 1.6   | -                     | V     |

| Signal-to-noise ratio                   | SNR                      | With an amplitude closed to the maximum |                | 58                  | 61    | 63                    | dB    |

| Spurious free dynamic range             | SFDR                     | -                                       |                | 55                  | 63    | 65                    | dB    |

| Common mode voltage                     | U                        | -                                       |                | -                   | 0.9   | -                     | V     |

| Duty cycle                              | DC                       |                                         |                | 45                  | 50    | 55                    | %     |

| Input high level voltage                | $V_{\mathrm{IH}}$        | For digital inputs                      |                | 0.7*V <sub>cc</sub> | -     | V <sub>cc</sub> +0.25 | V     |

| Input low level voltage                 | $V_{\rm IL}$             |                                         |                | -0.25               | -     | 0.3*V <sub>cc</sub>   | V     |