## 5 to 20MHz Intermediate frequency amplifier

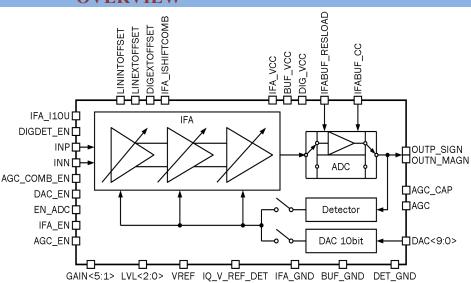

## **OVERVIEW**

180SMIC IFA 02 consists of 3-stages amplifier with tunable gain, AGC system, output buffer for differential analog output, analog-digital converter for 2-bits digital output. Each stage of the amplifier has differential input and output. Gain is sequentially reduced from the last stage to the first stage. Also gain can be fixed by the digital code DAC<9:0>. Output voltage supported by AGC system on differential load at 500Ohm or

1kOhm compounds: for sine waveform 200 mV (peak-to-peak); for noise signal 480 mV (peak-to-peak).

IP technology: SMIC CMOS 180 nm.

IP status: silicon proven.

Area: 0.88mm<sup>2</sup>.

## **ELECTRICAL CHARACTERISTICS**

| Parameter                                       | Symbol                 | Conditions                                                                                   | Value                        |                              |                           | T ] :4 a |

|-------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------|------------------------------|------------------------------|---------------------------|----------|

|                                                 |                        |                                                                                              | min                          | typ.                         | max                       | Units    |

| Supply voltage                                  | V <sub>CC_IFA</sub>    | -                                                                                            | 3.0                          | 3.15                         | 3.3                       | V        |

| Operating temperature range                     | $T_{j}$                | -                                                                                            | -40                          | +27                          | +85                       | °C       |

| Frequency range                                 | F                      | -                                                                                            | 5                            | -                            | 20                        | MHz      |

| Maximal gain                                    | G <sub>max</sub>       | -                                                                                            | 62                           | 70                           | 76                        | dB       |

| Noise figure                                    | NF                     | -                                                                                            | -                            | 5.7*                         | 7.6*                      | dB       |

| Group delay time ripple                         | RPAF                   | -                                                                                            | -                            | 2.9                          | 3.8                       | ns       |

| Differential output resistance                  | R <sub>IN</sub>        | -                                                                                            | 1550                         | 1960                         | 2500                      | Ohm      |

| Peak-to-peak voltage at the differential output | A <sub>p-p</sub>       | -                                                                                            | 180                          | 200                          | 226                       | mV       |

| Output logic-level low (digital outputs)        | $V_{OH\_dig}$          | For outputs OUT <sub>p/Sign</sub> , OUT <sub>n/Magn</sub> , with ADC mode. Load current 2 mA | V <sub>CC_IFA</sub> -<br>0.5 | V <sub>CC_IFA</sub> -<br>0.2 | V <sub>CC_IFA</sub>       | V        |

| Output logic-level high (digital outputs)       | $V_{\mathrm{OL\_dig}}$ | For outputs OUT <sub>p/Sign</sub> , OUT <sub>n/Magn</sub> , with ADC mode. Load current 2 mA | 0                            | 0.04                         | 0.2                       | V        |

| ADC capacity                                    | K                      | -                                                                                            | -                            | 1.5                          | -                         | bit      |

| Supply current                                  | $I_{cc}$               | Linear mode<br>ADC mode, 10 MHz                                                              | -                            | 3.4<br>4.9                   | 4<br>6.1                  | mA<br>mA |

| Stand-by current                                | I <sub>stb</sub>       | -                                                                                            | -                            | 0.01                         | 0.15                      | uA       |

| Input logic-level high                          | $V_{ m IH}$            | For digital inputs                                                                           | 0.7V <sub>CC_IFA</sub>       | -                            | V <sub>CC IFA</sub> +0.25 | V        |

| Input logic-level low                           | $V_{IL}$               |                                                                                              | -0.25                        | -                            | 0.3                       | V        |

Note:

Ver. 1.0 July 2020 www.ntlab.lt

<sup>\* -</sup> with voltage gain coefficient over 30 dB